Si estaba planeando una nueva compilación de PC en los últimos meses, la frase que pudo haber escuchado una y otra vez fue “espera a Skylake”. Bueno, Skylake está aquí, y la nueva arquitectura comprende la línea de CPU Core de sexta generación de Intel. Si aún no lo ha hecho, asegúrese de revisar nuestra revisión del procesador Intel Core i7-6700K y el chipset Z170.

Directamente al grano, el Core i7-6700K es el procesador de escritorio de cuatro núcleos más rápido de Intel hasta la fecha. Sin embargo, una cosa con la que no profundizamos demasiado son los gráficos integrados, y eso se debe a que Intel mantuvo un estricto control sobre la tecnología subyacente. Eso es, hasta ahora.

Y he aquí, hay un documento técnico en el sitio web de Intel que detalla la arquitectura informática de los gráficos “Gen9” de Intel. Es una actualización del documento técnico de Gen8, aunque se notan cambios de arquitectura específicos en Gen9 en todas partes.

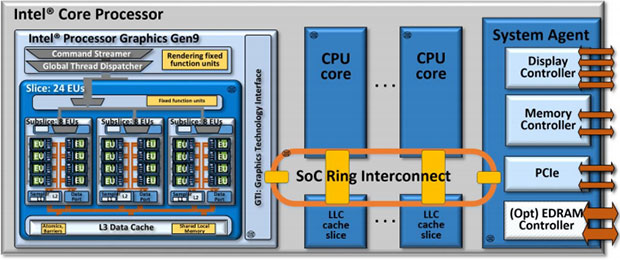

Al igual que con los procesadores Core anteriores, Skylake usa una arquitectura System-on-Chip (SoC), un término que se escucha con bastante frecuencia en el mundo móvil con respecto a chips como la serie Snapdragon de Qualcomm y la serie A personalizada de Apple. Específicos del 6700K son cuatro núcleos de CPU, Intel HD Graphics 530, LLC compartida, interfaces de memoria y E / S, y varios controladores, como se muestra arriba.

“Los procesadores Intel Core de sexta generación son SoC complejos que integran múltiples núcleos de CPU, gráficos de procesador Intel y potencialmente otras funciones fijas, todo en un solo chip de silicio compartido”, explica Intel. “La arquitectura implementa múltiples dominios de reloj únicos, que se han particionado como un dominio de reloj de núcleo por CPU, un dominio de reloj de gráficos de procesador y un dominio de reloj de interconexión en anillo. La arquitectura de SoC está diseñada para ser extensible para una gama de productos y aún así, permite un enrutamiento de cables eficiente entre los componentes dentro del SoC “.

La topología en anillo a la que hace referencia Intel es un bus integrado entre núcleos de CPU, cachés y gráficos. Es bidireccional y tiene 32 bytes de ancho con líneas separadas para diferentes tareas. Todas las transacciones de memoria del sistema fuera del chip que van hacia y desde los núcleos de la CPU y hacia y desde la porción de gráficos son facilitadas por la interconexión en anillo.

La topología en anillo a la que hace referencia Intel es un bus integrado entre núcleos de CPU, cachés y gráficos. Es bidireccional y tiene 32 bytes de ancho con líneas separadas para diferentes tareas. Todas las transacciones de memoria del sistema fuera del chip que van hacia y desde los núcleos de la CPU y hacia y desde la porción de gráficos son facilitadas por la interconexión en anillo.

Nada de esto es realmente nuevo, entonces, ¿qué hace que Gen9 sea especial? Aquí hay una descripción general de los cambios que Intel realizó específicamente en Gen9.

Refinamientos de jerarquía de memoria Gen9

El rendimiento de escritura coherente de SVM se mejora significativamente mediante las nuevas políticas de administración de caché de LLC. La capacidad de caché L3 disponible se ha aumentado a 768 Kbytes por segmento (512 Kbytes para datos de la aplicación). Se han aumentado los tamaños de las colas de solicitudes de L3 y LLC. Esto mejora la ocultación de la latencia para lograr un mejor ancho de banda efectivo contra el pico de arquitectura teórico. En Gen9 eDRAM ahora actúa como un caché del lado de la memoria entre LLC y DRAM. Además, el controlador de memoria EDRAM se ha trasladado al agente del sistema, junto al controlador de pantalla, para admitir la actualización de pantalla de baja latencia y eficiencia energética. Los muestreadores de texturas ahora admiten de forma nativa un formato NV12 YUV para compartir superficies mejoradas entre las API de computación y las unidades de función fija de medios.

Refinamientos de la capacidad informática Gen9

La preferencia de las aplicaciones informáticas ahora se admite a nivel de subproceso, lo que significa que los subprocesos de cómputo se pueden adelantar (y luego reanudar) a la mitad de su ejecución. operaciones atómicas de mínimo, máximo y comparar / intercambiar. Además, se mejora el rendimiento de todos los atómicos de 32 bits para escenarios de kernel que emitían múltiples atómicos consecutivos. La capacidad de punto flotante de 16 bits se mejora con soporte nativo para desnormales y subdesbordamiento gradual.Mejoras en la flexibilidad de la configuración del producto Gen9

Gen9 ha sido diseñado para permitir productos con 1, 2 o 3 cortes. Gen9 agrega nuevos dominios de reloj y control de energía para una administración de energía dinámica más eficiente. Esto puede mejorar particularmente los modos de reproducción de medios de baja potencia.

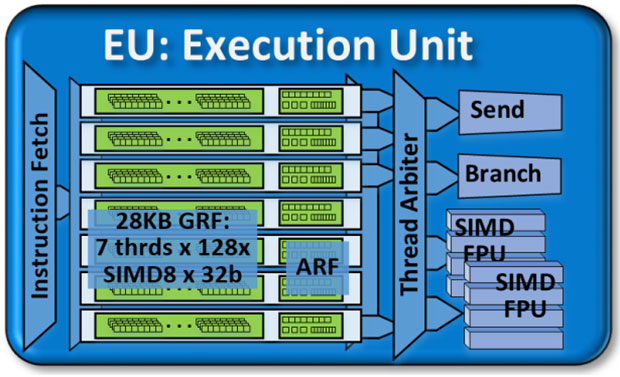

La Unidad de ejecución (UE) en los gráficos integrados de Skylake es similar al diseño Gen8. En este caso, cada Gen9 EU tiene siete subprocesos con los que trabajar, cada uno de los cuales presenta 128 registros de propósito general. Cada uno de esos registros puede almacenar 32 bytes accesibles como un vector de 8 elementos SIMD de elementos de datos de 32 bits.

En cada UE, un par de unidades de punto flotante SIMD (FPU) se encargan de las tareas de cálculo. Aunque Intel se refiere a ellos como FPU, son compatibles con el cálculo de punto flotante y entero: hasta cuatro operaciones de punto flotante o entero de 32 bits, o hasta ocho operaciones de punto flotante de 16 bits o entero de 16 bits. La integración de punto flotante de 16 bits también es nueva en Skylake / Gen9.

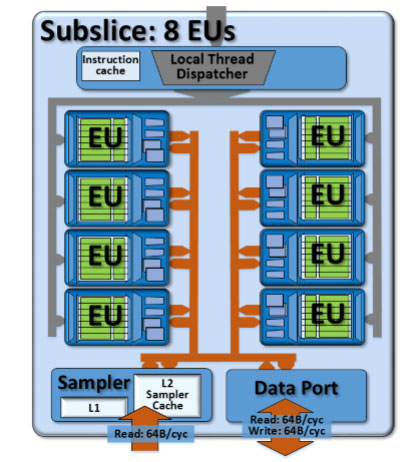

Profundizando un poco más, podemos ver la arquitectura de sublicencia de Intel en Gen9. Las matrices de EU se agrupan en una sublicencia, cada una de las cuales contiene su propia unidad de despachador de subprocesos local y sus propios cachés de instrucciones de apoyo. La mayoría de los productos Gen9 contienen ocho EU por sublicencia, aunque los arquitectos de productos pueden implementar con cualquier número de EU en múltiplos de la sublicencia anterior.

Con ocho EU y siete subprocesos, una sola sublicencia tiene recursos de hardware dedicados y archivos de registro para un total de 56 subprocesos simultáneos, junto con una unidad de muestreo y una unidad de gestión de memoria de puerto de datos. El puerto de datos admite operaciones de lectura / escritura eficientes para una variedad de accesos al búfer de propósito general, operaciones SIMD y acceso a memoria local compartida.

Intel creó una arquitectura gráfica escalable con múltiples diseños de productos potenciales diferentes. Para Intel Core i7-6700K con Intel HD Graphics 530, el diseño del producto consiste en una sola porción con tres sublicencias para un total de 24 EU.

Esa no será la implementación más poderosa de los gráficos integrados de Skylake. Como vimos en nuestra evaluación 6700K, los gráficos HD 530 no son tan rápidos como los Iris Pro 6200 de Intel en pruebas y pruebas de juegos como Cinebench. Sin embargo, es un buen punto de partida.

En la imagen que se muestra arriba, puede ver otro diseño potencial, este tiene tres cortes, cada uno de los cuales tiene tres sublices para un total de 72 EU.

Es esta implementación la que más nos entusiasma. Si bien el rendimiento de los gráficos del 6700K resultó útil, proporcionó un modesto aumento en el rendimiento con respecto al producto de la generación anterior. El diseño anterior se manifestará en GT4 / e y será la solución de gráficos Intel HD integrada más rápida de Intel hasta la fecha. No esperamos que GT4 / e acabe con el mercado de las tarjetas gráficas discretas, pero tiene la posibilidad de competir con las tarjetas gráficas de gama baja.