Microarquitectura Intel Tremont: orientación a clientes, centros de datos, redes 5G e IoT

A fines del año pasado, en su evento del Día de la Arquitectura, Intel reveló una nueva microarquitectura de bajo consumo, con nombre en código Tremont, que potenciaría una variedad de procesadores y SoC dirigidos a productos en los mercados de clientes, centros de datos, redes 5G e Internet de las cosas. Si bien Intel reveló el nombre en clave y mostró un SoC basado en Foveros con Tremont, con nombre en código Lakefield, no profundizó en la microarquitectura ni discutió su funcionamiento interno.

Hoy, sin embargo, en la Linley Fall Processor Conference que se está llevando a cabo actualmente, Intel analizó Tremont en profundidad y reveló sus características principales, mejoras de microarquitectura, nuevas instrucciones y niveles de rendimiento esperados.

La arquitectura Tremont de Intel es una diferencia significativa de sus predecesores

Tremont es una microarquitectura x86 de 10 nm de baja potencia que es la sucesora de Goldmont Plus, que se utiliza en los actuales procesadores Atom, Pentium Silver y algunos procesadores de la serie Celeron. Tremont está destinado a paquetes compactos de bajo consumo e incorpora una serie de actualizaciones de ISA, funciones de seguridad mejoradas, administración de energía más avanzada y ofrece mejoras significativas de IPC (Instrucciones por ciclo) de generación a generación en comparación con el bajo consumo actual de Intel. Arquitecturas x86.

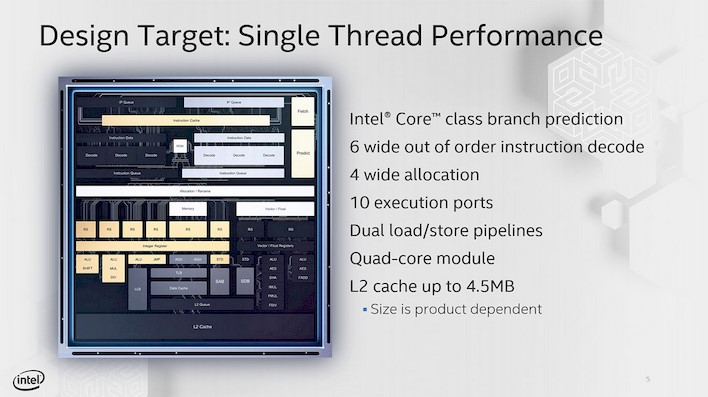

Tremont también es una desviación significativa de Goldmont Plus y sus predecesores. Tremont cuenta con un predictor de rama Intel Core-Class, con decodificador de instrucciones fuera de orden de 6 anchos en el front-end, con 4 amplia asignación, 10 puertos de ejecución en el back-end y canalizaciones de almacenamiento y carga dual. Tremont está diseñado con hasta cuatro núcleos en mente, con hasta 4.5 MB de caché L2, pero la configuración real de la caché dependerá del diseño específico del producto.

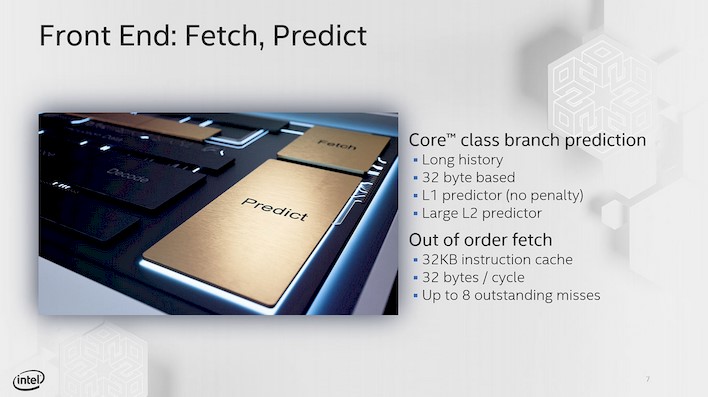

La predicción de ramas en Tremont tiene un historial de soporte y se basa en 32 bytes. El predictor L1 no tiene penalización de rama y el predictor L2 es más grande que los productos de generaciones anteriores. El buscador cuenta con una caché de instrucciones de 32 KB (32 bytes por ciclo) que puede manejar hasta 8 fallas pendientes y aún permitir que el procesador continúe ejecutando instrucciones.

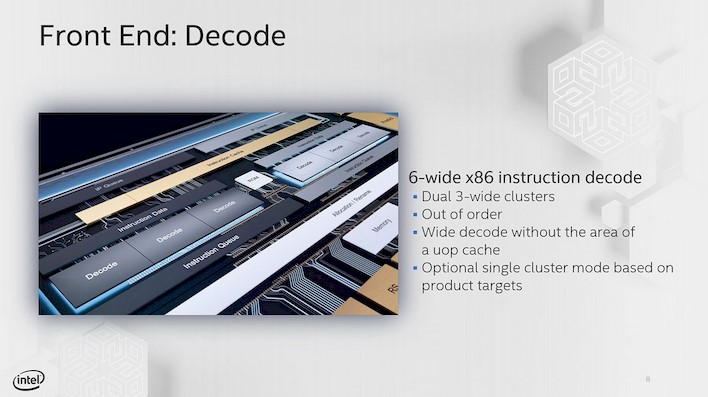

El decodificador de instrucciones x86 de 6 anchos en Tremont se divide en grupos duales de 3 anchos. Como se mencionó, es un diseño desordenado con amplio soporte de decodificación, sin usar área para un caché de uOP. El diseño también se puede reducir a una configuración única de 3 anchos, según el diseño del producto de destino.

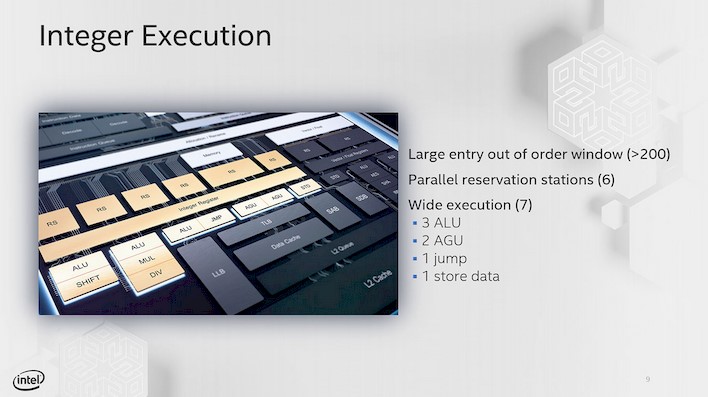

Tremont tiene una ventana fuera de servicio> 200 (208, específicamente), con 6 estaciones de reserva paralelas. Cuenta con 3 ALU, 2 AGU, 1 puerto de salto y 1 puerto de datos de almacenamiento.

También hay dos unidades AES 128b presentes en Tremont, que pueden manejar una sola instrucción SHA256 para cargas de trabajo de cifrado en solo 4 ciclos. El nuevo apoyo de instrucción de Galois Field (GF) también está presente. Hay dos estaciones de reserva paralelas en el diseño, con tres puertos de ejecución.

Tremont cuenta con canalizaciones de carga / almacenamiento dual, con 32 KB de caché de datos (3 ciclos) y un búfer de búsqueda de traducción de segundo nivel de 1024 entradas.

La caché L2 de Tremont se comparte entre los núcleos y puede escalar desde 1,5 MB hasta 4,5 MB. También hay soporte de caché de último nivel incorporado, que es el primero en los diseños de bajo consumo de Intel, aunque no se implementará en todos los diseños. La tecnología Intel Resource Directory incorpora QoS para L2 y LLC para optimizar el rendimiento y el uso del ancho de banda.