Intel celebró ayer un Día de la Arquitectura en Los Altos, donde reveló una serie de detalles sobre las arquitecturas de CPU y GPU de próxima generación y las tecnologías de procesos de fabricación. Además de las divulgaciones técnicas divulgadas a un grupo exclusivo de asistentes, Intel también habló sobre un cambio en el modelo de diseño e ingeniería de la empresa basado en seis pilares estratégicos: proceso, arquitectura, memoria, interconexión, seguridad y software, que espera le permitirá abordar mejor las necesidades del panorama informático actual en el futuro.

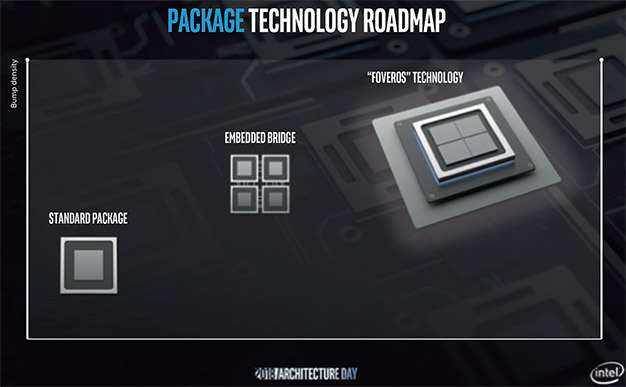

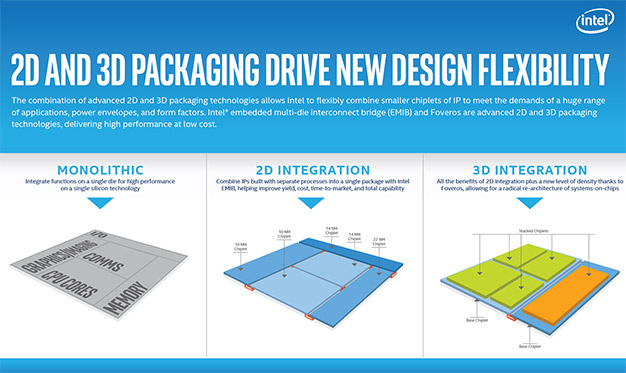

Además de las noticias sobre la arquitectura y la hoja de ruta, Intel también habló sobre una nueva y muy interesante tecnología de empaque en 3D a la que llama “Foveros”, que permitirá el primer apilado en 3D de lógica compleja de la industria.

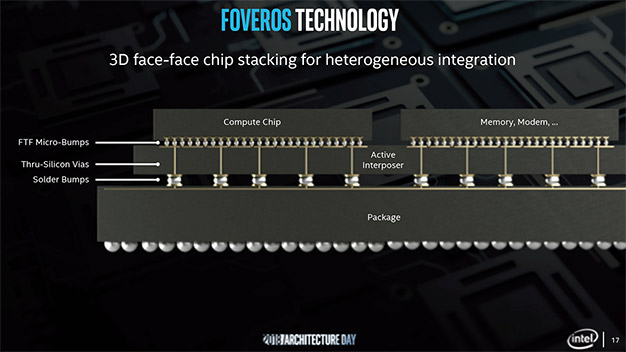

Ahora, el apilamiento 3D y los circuitos integrados 3D no son tecnologías nuevas; han estado empleados durante años. Foveros, sin embargo, es algo diferente. Foveros lleva las cosas un paso más allá y permitirá la integración lógica sobre lógica. Foveros va más allá del apilamiento de troqueles tradicional con intercaladores pasivos y memoria apilada y funcionará con circuitos lógicos de alto rendimiento, como núcleos de CPU, GPU, procesadores de IA y similares.

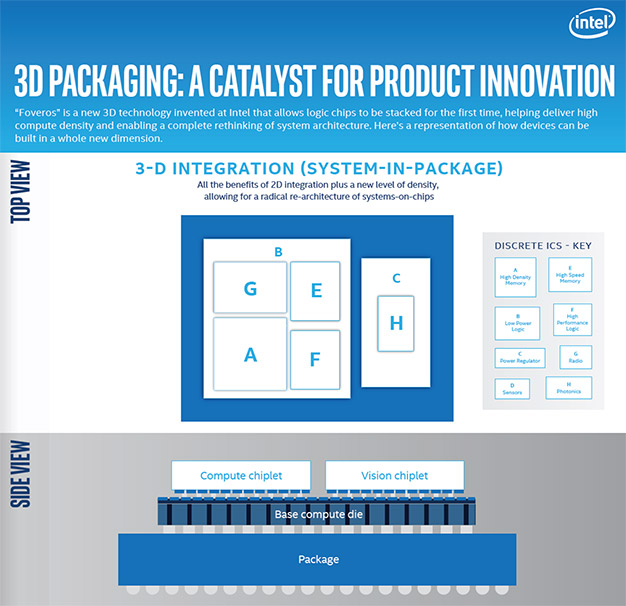

Debido a sus capacidades únicas, Foveros debería marcar el comienzo de algunos diseños de chips interesantes. Por ejemplo, con Foveros, tanto el silicio de alto rendimiento / alta densidad como el de bajo consumo se pueden combinar en un solo dispositivo. Como tal, junto con la tecnología de empaquetado 2D EMIB (Embedded Multi-die Interconnect Bridge) de Intel, Foveros permitirá a los diseñadores mezclar y combinar bloques IP con varios elementos de memoria, sensor y E / S, para crear nuevos dispositivos y formularios. factores.

Con Foveros y EMIB, los dispositivos compuestos por “chiplets” más pequeños, con SRAM, E / S y circuitos de suministro de energía, pueden ser parte de un dado base, y se pueden apilar chiplets lógicos de alto rendimiento adicionales en la parte superior mediante un ancho de banda alto vías de silicio.

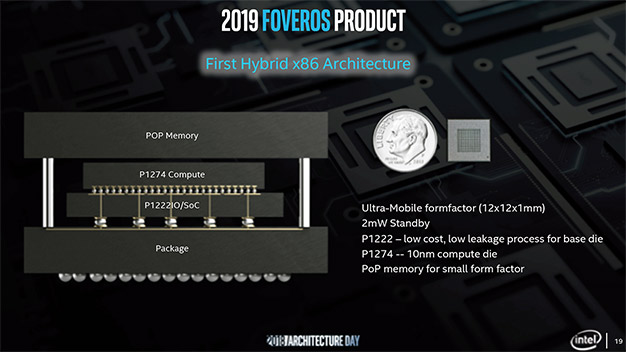

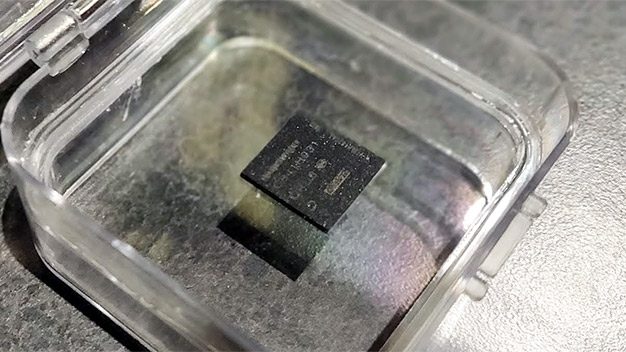

Según Intel, espera lanzar una gama de productos que aprovechen Foveros, a partir de la segunda mitad de 2019. El primer producto basado en Foveros, que en realidad se demostró en vivo en el evento, combinará una computadora de alto rendimiento de 10nm apilada. chiplet con un troquel base de 22 nm de baja potencia.

El SoC de próxima generación que se mostró en el evento de Intel estaba compuesto por 5 núcleos en total (cuatro núcleos de baja eficiencia energética y un núcleo de alto rendimiento) con gráficos, E / S y memoria POP, todo en un solo chip de 12x12x1 mm que usa solo 2 mW de energía en espera. La demostración mostró que se reproducía un video 4K y se reducía a 1080p en el núcleo de bajo consumo, en Windows 10, con un bajo uso de la CPU. Al cambiar el tamaño del video (o presionar la tecla de Windows) sin problemas, se desbloqueó el núcleo de alto rendimiento, pero no se revelaron otros puntos de referencia o datos de rendimiento.

En total, Foveros y EMIB permitirán a Intel no solo mezclar y combinar chiplets producidos con diferentes tecnologías de proceso, mejorar los rendimientos, el costo y el tiempo de comercialización, sino también empaquetarlos en múltiples dimensiones en dispositivos individuales, para aumentar la densidad y habilitar nuevos factores de forma. Las tecnologías parecían prometedoras y ver dispositivos ya en funcionamiento fue alentador, por decir lo menos.