Intel anunció su familia de procesadores escalables Xeon a principios de mayo, con la microarquitectura Skylake-SP. Esos procesadores aún no se han lanzado oficialmente, pero hoy el gigante de los chips está revelando una de las tecnologías clave que se aprovechan en la familia de procesadores escalables Xeon. Se ha diseñado una nueva arquitectura de interconexión de malla para aumentar el ancho de banda entre los elementos en el chip, mientras que al mismo tiempo disminuye la latencia y mejora la eficiencia energética y la escalabilidad. En una publicación de blog en el sitio web de la compañía, Akhilesh Kimar, Skylake-SP CPU Architect explica: La tarea de agregar más núcleos e interconectarlos para crear un procesador de centro de datos de múltiples núcleos puede parecer simple, pero las interconexiones entre los núcleos de la CPU, la jerarquía de memoria y los subsistemas de E / S proporcionan rutas críticas entre estos subsistemas que requieren una arquitectura cuidadosa. Estas interconexiones son como una carretera bien diseñada con el número correcto de carriles y rampas en lugares críticos para permitir que el tráfico fluya sin problemas … “

Arquitectura Intel Ring Bus En los procesadores Xeon de muchos núcleos de la generación anterior, Intel ha utilizado una arquitectura de interconexión en anillo para vincular los núcleos de la CPU, la memoria caché, la memoria y varios controladores de E / S en los chips. Sin embargo, a medida que ha aumentado la cantidad de núcleos en los procesadores, la memoria y el ancho de banda de E / S, se ha vuelto cada vez más difícil lograr la máxima eficiencia con una interconexión de anillo, porque una arquitectura de anillo podría requerir que los datos se envíen a través de tramos largos ( relativamente hablando) del anillo para llegar a su destino previsto. La nueva arquitectura de malla aborda esta limitación interconectando elementos en el chip de una manera más generalizada, para finalmente aumentar el número de vías y mejorar la eficiencia.

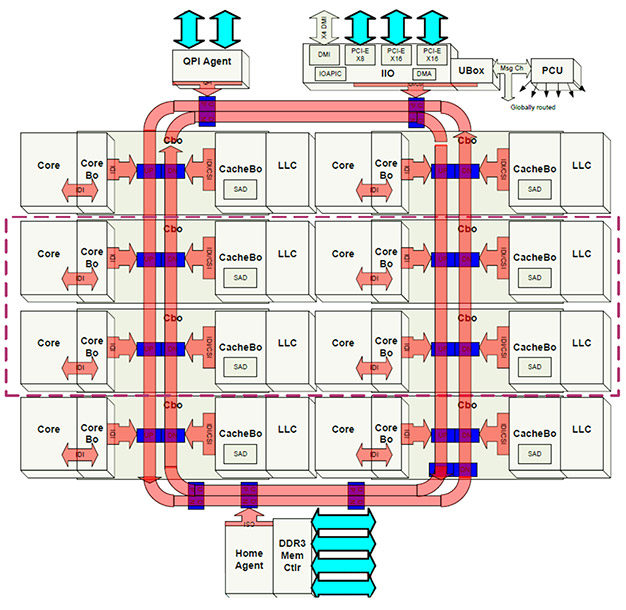

Arquitectura de interconexión de malla Intel Arriba hay una representación visual de la nueva arquitectura de malla. En el diagrama, los núcleos de procesador, los bancos de caché en chip, los controladores de memoria y los controladores de E / S están organizados en filas y columnas. Los cables e interruptores conectan los diversos elementos del chip y proporcionan rutas más directas que la arquitectura de interconexión de anillo anterior. La naturaleza de una malla también permite que se implementen muchas más vías, lo que minimiza aún más los cuellos de botella y también permite a Intel operar la malla a una frecuencia y voltaje más bajos, sin dejar de ofrecer un alto ancho de banda y baja latencia.

Kimar también dice en la publicación: “El marco de interconexión en chip escalable y de baja latencia también es fundamental para la arquitectura de caché compartida de último nivel. Esta gran caché compartida es valiosa para aplicaciones de servidor complejas de múltiples subprocesos, como bases de datos, simulaciones físicas complejas, aplicaciones de red de alto rendimiento y para alojar múltiples máquinas virtuales. Las diferencias de latencia insignificantes al acceder a diferentes bancos de caché permiten que el software trate los bancos de caché distribuidos como una gran caché unificada de último nivel “.

Junto con la nueva malla, que mejora la conectividad y la topología de la interconexión en chip, Intel está implementando una arquitectura modular con sus procesadores escalables Xeon para recursos que acceden a la memoria caché, E / S y CPU remotas en el chip. Estos recursos se distribuyen por todo el chip, por lo que se minimizan los “puntos calientes” en las áreas que podrían tener cuellos de botella. Intel afirma que el mayor nivel de modularidad con la nueva arquitectura permite que los recursos disponibles escalen mejor a medida que aumenta la cantidad de núcleos de procesador.